(An ISO 3297: 2007 Certified Organization) Vol. 5, Issue 6, June 2016

# Analysis of THD in Asymmetrical Multilevel Inerter Using a Novel Topology

Suhirthana. $S^1$ , Jayasudha. $K^2$

P.G Student, Department of EEE, J.J. College of Engineering and Technology, Trichy, Tamil Nadu, India<sup>1</sup>.

Assistant Professor, Department of EEE, J.J. College of Engineering and Technology, Trichy, Tamil Nadu, India<sup>2</sup>.

**ABSTRACT:** Synchronous optimal pulse width modulation (SOP) allows low switching frequency modulation of construction electrical converter for medium-voltage high-power industrial ac drives while not compromising on total harmonic distortion (THD).the scope of experiment was to operate a 13-level cascade inverter of induction motor drive at an average device change frequency restricted to rated fundamental frequency by victimization SOP technique. To reduce the number of separate dc sources, a three-level diode clamped converter was used as a cell in the 13-level cascade inverter. Using SOP technique, optimal 13-level waveforms were obtained by offline optimization presumptuous steady-state operation of the induction machine. The switching angles for every semiconductor switch are then obtained from best 13-level waveforms primarily based on the criteria to attenuate the switching frequency similarly as unbalance in dc-link capacitor voltages.

KEYWORDS: Multilevel inverter, Medium-voltage ac drives, THD,

### I. INTRODUCTION

Multilevel converters area unit currently well-established and standard resolution for medium and high-voltage, high power applications. Theadvantages of structure converters over two-level convertersare higher voltage operative capability with medium voltagesemiconductor devices, improved output voltages with less harmonic distortion, reduced common-mode voltage, near curving input currents, smaller input and output filters, increased potency due to chance of low change operation, reduced electromagnetic interference issues and doablefault-tolerant operation. In addition, the torque ripplealso reduces as range of levels will increase in case of structureinverter fed ac drives. In high-power applications, the switchinglosses contribute to major portion of total device losses andthus low change frequency operation is necessary to realize higher potency. However, minimizing switching frequency will increase the harmonic distortion. Therefore, the challenge is tominimize the harmonic distortion while reducing the changefrequency. Presently, the most popular topologies area unit diode-clampedor neutral-point-clamped (NPC), capacitor-clamped or flyingcapacitor (FC) and cascaded H-Bridge (CHB). The CHBtopologies are most popular for higher-level converters due to demandof least number of elements and ease of management compared to other topologies. In addition, modularized circuitlayout and packaging is also doable with CHB topology as a result of each level has similar structure. However, one majordrawback of this topology is demand of multiple numbers of dc-sources, which is not possible in several applications. One of the methods for reducing the quantity of dc sources is to exchangeH-Bridge cell with NPC or FC converters. However, animportant issue with the topologies having agency or FC convertersis voltage unbalance of dc-link capacitors that further ads to harmonic distortion of output voltage waveforms. An auxiliarycapacitor-based balancing approach has been plannedto equalize the dc-link capacitor voltages for agency five-level converter. Several low change frequency modulation techniques havebeen proposed for dynamical applications. A new modulationmethod for standard structure convertor operative at elementaryswitching frequency whereas with success eliminating fifth harmonic.

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 6, June 2016

#### **II.PROPOSED 13 LEVEL CASCADE INVERTER**

Synchronous optimal pulse width modulation (SOP) technique is an rising technology to scale back switch frequency without compromising on harmonic distortion. Unlike SHE method, SOP takes into account all possible lower order harmonic components and determines switch angles thus as to keep the total harmonic distortion (THD) of output voltage or current waveforms within limits. SOP consists of Fourier series analysis of output voltage or current waveforms to model equations using switch angles as variables and their optimization to reduce doctorate. All the calculations are computed offline assuming steady state operative conditions.SOP generates optimal switch pulse patterns of semiconductor devices in a multilevel electrical converter. Synchronized PWM is used in low-switching frequency applications where carrier signal at frequency (fs ) and sinusoidal management signal at frequency (f1 ) are synchronized with every alternative, i.e., fs f1 is an integer in order to eliminate sub harmonic frequencies that square measure undesirable in many applications. Synchronized PWM results in lower number of switch instants per elementary amount and even a little variation in these switch angle values can have sizable influence on the harmonic distortion of output voltage. Optimization ways square measure urged to predetermine switching angles offline to scale back harmonic distortion. The recalculated switching angles square measure holds on and retrieved throughout real-time operation.

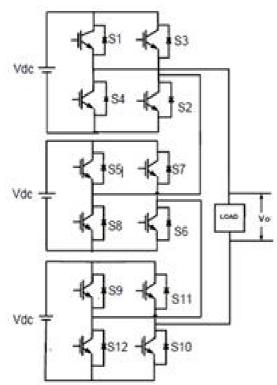

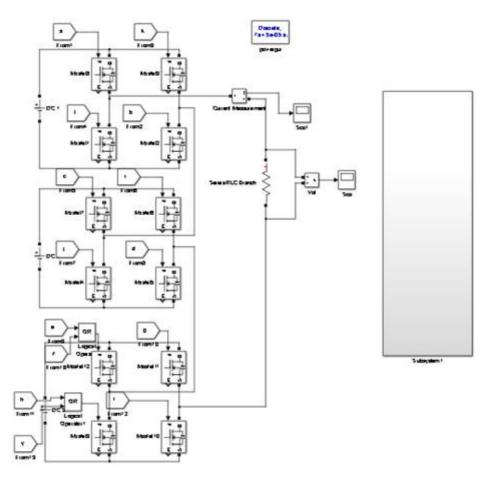

Figure 1: proposed circuit diagram

Asymmetrical dual bridge MLDCLI is one of the foremost necessary topology within the family of multilevel electrical converter (MLI). It requires least range of element compare to cascade H—bridge multilevel electrical converter and symmetrical twin bridge dc-link electrical converter. It consist two cell of H-bridge, first H-bridge work to increase the amount of the dc-link voltage and second H-bridge provide bi-directional power flow through the load. Each cell has designed to four switches Associate in Nursing an connected auxiliary switch is series with dc source, combination shunted through an opposed parallel diode. In this topology switch is used IGBT.DC voltage source area unit contemplate to be identical since all of them area unit batteries, solar cell, etc. it has two separatedc supply and totally

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 6, June 2016

different voltage. Asymmetrical seven level dual bridge dc-link multilevel electrical converter will operates in totally different modes witch area unit given. When switch S1, S2,S7 and S8 turned ON, an output voltage is V0 obtained with diode D1 operating as forward-bias. When switches S1, S2, S6, S8 and S9 are turned ON, an output voltage isV1 obtained with diode D1 working as reversed bias. When switch S1, S2, S7,S8 and S9 are turned ON, an output voltage is V0+V1 obtained with D1 operating as reversed-bias. When switch S1, S2, S6, S6 and S8 are turned ON, an output voltage is '2ero'' obtained for ''zero'' level with diode D1 working as forward-bias. When switch S3, S4, S7andS8 are turned ON, an output voltage is ''zero'' obtained with diode D1 working as forward-bias. When switch S3, S4, S6,S8 and S9 are turned ON, an output voltage is -V0 obtained with diode D1 working as forward-bias. When switch S3, S4, S6,S8 and S9 are turned ON, an output voltage is -V1 obtained with diode D1 operating as reversed-bias. S4, S7,S8 and S9 are turned ON, an output voltage is -V1 obtained with diode D1 operating as reversed-bias. When switch S3, S4, S6,S8 and S9 are turned ON, an output voltage is -V1 obtained with diode D1 operating as reversed-bias. When switch S3, S4, S7,S8 and S9 are turned ON, an output voltage is -(V0+V1) obtained with diode D1working as reversed-bias. For operation of seven level V0:V1= (50:100) V along with positive and negative cycle. The pair of switch S1 and S2 is used for positive half cycle, switch S3 and S2 is used for negative half cycle. If we take V0 = fifty = Vdc than V1= one hundred fifty =3Vdc.Cause of asymmetrical dc voltage source decreasing the switch losses, increasing the efficiency and eliminating the resultant effects of de-rating. Asymmetrical dual bridge dc-link structure electrical converter will be expressed victimization the relation 2(2n+1)+1, where n is the range of voltage supply excluding V0.

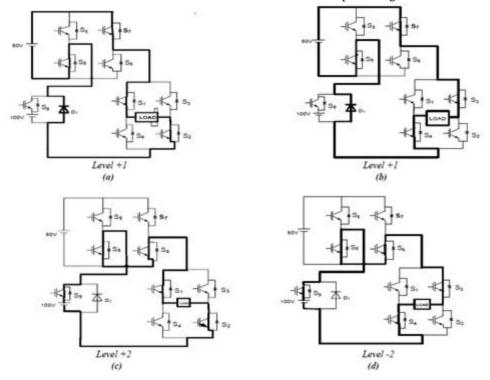

#### **III.OPERATING MODES**

For convenience to explain the in operation modes for varied levels, the dc link structure are represented by mounted dc supply in the coming diagrams. The operation for each story of a 13 level inverter with V0:V1 = (50:100) V on with positive and negative [\*fr1] cycles is explained pictorially through +3 level to -3 level. It will be seen from Figure nine. The try S1–S2 or pair S3–S4 in the H-bridge alternately is required to require extracting the primary level of the output voltage and goes through a similar sequence for other levels. The form of the output voltage shown in Figure ten clearly indicates the devices that conduct for the various levels of the output voltage.

(An ISO 3297: 2007 Certified Organization)

Vol. 5, Issue 6, June 2016

Figure 2 a,b,c,d,e,f: operating modes of proposed multilevel converter

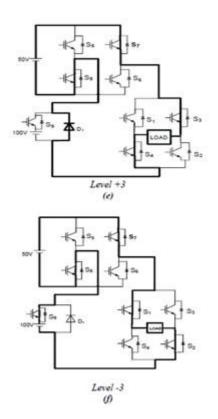

### **IV.CONTROL AND MODULATION STRATEGIES**

**Phase opposition disposition pulse width modulation (POD PWM)**:-In POD PWM strategy all (N-1) carriers signal are same part to every different higher than the zero-axis with frequency and amplitude but carrier wave reduced than zero-axis is 1800 out of part to higher than zero-axis carrier wave shape.

Figure 3:phase modulation techniques

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 6, June 2016

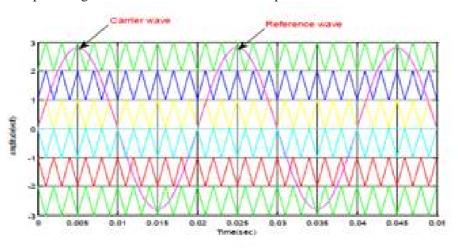

#### V.SIMULATION ANALYSIS AND RESULT

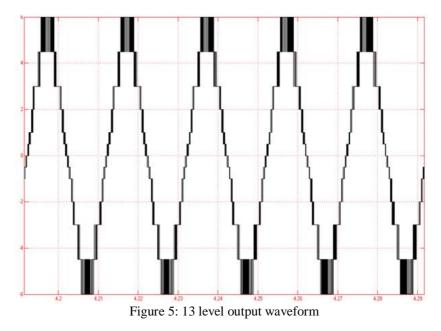

The proposed topology model of single-phase MLI. Table II shows its switching schemes and table I Comparison in terms of power components used for completely different level. The simulation parameters are as following R= ten ohm, L= 0.01mH and DC source V1 and V2 is 50V, 100V, respectively, carrier signal frequency is 4 kHz; doctor's degree area unit shown in Figure 12. The harmonic spectrum is carried out by using the FFT analysis in MATLAB/simulink.

Figure 4:simulation circuit of proposed multilevel inverter

(An ISO 3297: 2007 Certified Organization) Vol. 5, Issue 6, June 2016

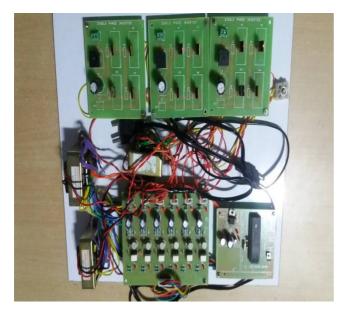

### VI.PROTOTYPE MODEL

The proposed technique has been implemented for controlling a 13-level cascade inverter feeding a 1.5-kW induction motor. One more necessary criterion whereas distribution changes angles is to attenuate the most device change frequency of every semiconductor device. the heartbeat range N determines the quantity of change transitions of the nine-level potential and every transition is being caused by a transition in one among four three level NPC inverters. The entire range of change transitions in turn decides the change frequency of conductor, so the pulse range ought to be divided equally among all the four three-level inverters.

Figure 6a:hardware image

(An ISO 3297: 2007 Certified Organization) Vol. 5, Issue 6, June 2016

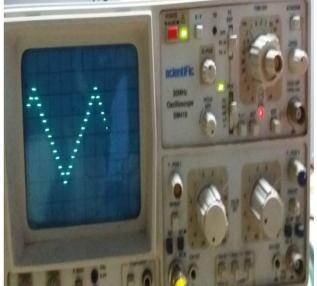

Figure 6c: 13 level sine wave

Figure 6d: 13 level

#### **VII.CONCLUSION**

An MLDCLI structure fittingly designed mistreatment a twin bridge configuration has been offered with a read to reduce the quantity of power switches to synthesize Associate in nursing increasing level of output voltages. The topology has been prepared mistreatment Associate in nursing acceptable selection of voltage ratios between the constituent parts in the module. The acquirement of the desired results has been found to feature a feather to vindicate the technology revolution in progress. The higher quality of output voltage which will be taken out using the new structure can go a long approach in insinuating bigger horizons of power converter interfaces in the machine-driven world.

#### REFERENCES

[1] Rodriguez J, La Jih-Sheng, Peng Fang Zheng. Multilevel inverters: a survey of topologies, controls, and applications. IEEE Trans Ind Electron 2002; 49:724–38.

[2] Lai Jih-Sheng, Peng Fang Zheng. Multilevel converters – a new breed of power converters. IEEE Trans Ind Appl 1996; 32:509–17.

[3] Tolbert LM, Peng Fang Zheng, Habetler TG. Multilevel converters for large electric drives. IEEE Trans Ind Appl 1999; 35:36-44.

[4] Stemmler H, Guggenbach P. Configurations of high-power voltage source inverter drives. In: Proceedings of IEEE international conference, vol. 5; 1993. p. 7–14.

[5] Fang Zheng Peng, Jih-Sheng Lai, McKeever J, VanCoevering J. A multilevel voltage-source converter system with balanced Dc voltages. In: Proceedings of IEEE international conference, vol. 2; 1995. p. 1144–50.

[6] Nabae A, Takahashi I, Akagi H. A new neutral-point clamped PWM inverter.IEEE Trans Ind Appl 1981; 17:518 23.

[7] Manjrekar MD, Steimer PK, Lipo TA. Hybrid multilevel power conversion system: a competitive solution for highpower applications. IEEE Trans Ind Appl 2000; 36:834–41.

[8] Meynard TA et al. Multicell converters: derived topologies. IEEE Trans Ind Electron 2002; 49:978-87.

[9] Carpita M, Marchesoni M, and Pellerin M, Moser D. Multilevel converter for traction applications: small-scale prototype tests results. IEEE Trans Ind Electron 2008; 55:2203–12.

[10] Choi NS, Cho GC, Cho GH. Modeling and analysis of a static VAR compensator using multilevel voltage source inverter. In: Proceedings of IEEE international conference 1993; p. 901–8.

[11] Shuai Lu, Corzine KA. Advanced control and analysis of cascaded multilevel converters based on P-Q compensation. IEEE Trans Ind Electron2007; 22:1242-52.

[12] Bernet S. Recent developments of high power converters for industry and traction applications. IEEE Trans Ind Electron 2000; 15:1102–17.

[13] Krug D, Bernet S, Fazel SS, Jalili K, Malinowski M. Comparison of 2.3 KVmedium-voltage multilevel converters for industrial medium-voltage drives. IEEE Trans Ind Electron 2007; 54:2979–92.

[14] Moreno-Munoz A, De-La-Rosa JJG, Lopez-Rodriguez MA, Flores-Arias JM, Bellido-Outerino FJ, Ruiz-de-Adana M. Improvement of power quality using distributed generation. Int J Electr Power Energy Syst 2010; 32(10):1069 76.

[15] Senthil Kumar N, Gokulakrishnan J. Impact of FACTS controllers on the stability of power systems connected with doubly fed induction generators. Int J Electr Power Energy Syst 2011; 33(5):1172–84.

(An ISO 3297: 2007 Certified Organization)

#### Vol. 5, Issue 6, June 2016

[16] Munduate A, Figueres E, Garcera G. Robust model-following control of a three level neutral point clamped shunt active filter in the medium voltage range. Int J Electr Power Energy Syst 2009; 31(10):577–88.

[17] EL- Kholy EE, EL-Sabbe A, El-Hefnawy A, Mharo HM. Three-phase active power filter based on current controlled voltage source inverter. Int J Electr Power Energy Syst 2006; 28(8):537–47.

[18] Gui-Jia Su. Multilevel dc-link inverter. IEEE Trans Ind Appl 2005; 41: 848-54.

[19] Marchesoni M, Tenca P. Diode-clamped multilevel converters: a practicable way to balance dc-link voltages. IEEE Trans Ind Electron 2002; 49:752-65.

[20] Yuan Xiaoming, Stemmler H, Barbi I. Investigation on the clamping voltage self-balancing of the three-level capacitor clamping inverter. In: Proceedings of IEEE international conference vol. 2; 1999 p.1059–64.