(A High Impact Factor & UGC Approved Journal) Website: <u>www.ijirset.com</u> Vol. 6, Issue 8, August 2017

# A Smooth Strategy for Outline of Low Power Successive Framework Utilizing Multi Bit Flip-Tumble

B.Hema Latha

Assistant Professor, Department of Electronics and Communication Engineering, Anurag Group of Intuitions, Hyderabad, Telangana, India

**ABSTRACT**: The real unique power customers in processing and buyer hardware items is thesystem's clock flag, normally in charge of 30%– 70% of the aggregate dynamic power utilization. Clock gatingis a prevalent strategy utilized for control sparing. The Information driven clock gating is utilized for lessen powerconsumption in synchronous circuits .Regular clock gating is utilized for control sparing. However clock gatingstill leaves bigger measure of repetitive clock beats. Multibit flip-slump is additionally used to diminish powerconsumption .Utilizing of Multibit Flip-Flounder strategy is to dispense with the aggregate inverter number by sharing theinverters in the flip-tumble .Mix of Multibit Flip-Slump with Information driven clock gating will increment thefurther control sparing. Xilinx programming apparatus and quatrus II for control examination is utilized for executing thisproposed framework.

**KEYWORDS**: Data Driven clock gating

### I. INTRODUCTION

The information of computerized frameworks are normally put away in flip-flops (FFs),each of which has its own inner clock driver. In an endeavor toreduce the clock control, a few FFs can be assembled into a modulecalled a multibit FF (MBFF) that houses the clock drivers of allthe basic FFs. We indicate the gathering of kFFs into a MBFFby a k-MBFF. Kapoor et al. [1] revealed a 15% lessening of the add up to dynamic power in a 90-nm processor outline. Electronicdesign robotization apparatuses, for example, Rhythm Free, bolster MBFFcharacterization.

The advantages of MBFFs don't want free. By sharing commondrivers, the clock slew rate is corrupted, therefore causing a largershort-circuit ebb and flow and a more extended clock-to-Q engendering postpone tpCQ.To cure this, the MBFF inward drivers can be reinforced at thecost of some additional power. It is in this manner prescribed to apply theMBFF at the RTL configuration level to dodge the planning conclusion hurdlescaused by the presentation of the MBFF at the backend outline stage.Due to the way that the normal information to-clock flipping proportion of FFs little, which as a rule ranges from 0.01 to 0.1 [2], the clockpower investment funds dependably exceed the short out power punishment of thedata flipping.

A MBFF gathering ought to be driven by coherent, basic, andFF action contemplations. While FFs gathering at the format levelhave been contemplated completely, the front-end ramifications of MBFFgroup size and how it influences clock gating (CG) has pulled in littleattention. This short reacts to two inquiries. The first is the thing that theoptimal bit variety k of information driven clock-gated (DDCG) MBFFsshould be. The second is the manner by which to augment the power reserve funds basedon information to-clock flipping proportion (likewise named movement and information togglingprobability).

In existing framework control lessening is accomplished by utilizing clock gating. With clock gating, the Clock signals are increase with an AND door rationale to expressly predefined empowering signal. In any case, this clock gating still leaves huge number of repetitive clock beats. Albeit significantly expanding outline efficiency, such instruments require the work of a long chain of programmed combination calculations, from enlist exchange level (RTL) down to entryway level and net rundown. Sadly, such mechanization prompts a huge number of superfluous clock flip, along these lines expanding the quantity of squandered time beats at flipflops (FFs) as appeared in this paper through a few mechanical cases. Subsequently, advancement of programmed and viable strategies to decrease this wastefulness is alluring. In the continuation, we will utilize the terms flipping, exchanging, and action conversely.

(A High Impact Factor & UGC Approved Journal)

Website: <u>www.ijirset.com</u>

#### Vol. 6, Issue 8, August 2017

#### II. RELATED WORK

Several dynamic power control techniques are adopted in VLSI circuits out of which the most important oneis clock gating.[5] uses multiple deliver voltages to reduce clock tree energy. The incoming, high voltage clocksignal is downscaled through a low-voltage buffer level. The low-V<sub>dd</sub> signal is then propagatedthroughout the circuit, and regenerating factors (e.g., buffers) are inserted into the tree structure to make sure theappropriate pace and slew rate of the transitions. Finally, the original high-voltage is restored thru level shifters before the clock alerts feed the flip-flops. In [3] Clock Distribution the use of Multiple Voltages reduces the rate of buffering and voltageconverters this is crucial inside the electricity discount technique implemented the use of more than one supply voltages. Themethod supplied with the aid of Pangjung and Sapatnekar addresses this predicament with the aid of providing an extra sophisticatedset of rules for introducing buffers into the clock tree and for putting the low-to-high voltage shifters, which areno longer necessarily positioned right in the front of the flip-flops. The set of rules considers the opportunity of buffer insertion after each step of backside-up subtree merging. In the diversion of keeping the skew very near zero, the set of rules guarantees that the range of regenerating factors is equalized along any root-to-sink paths ofthe tree. However, no matter the stable theoretical basis of this answer, experimental effects confirmed very smalldifferences with the clock bushes generated through the approach the usage of multiple supply voltages In [2] makes a specialty of Interconnect Power, i.e. Power dissipation due to the switching of interconnectioncapacitances, which can be a part of the full switched capacitance of every internet- Cj. Applying wire capacitancediscount techniques to a small percent of the wires can keep the majority of the interconnect energy.

Capacitance may be reduced by means of interconnect reduction and increasing interconnect spacing thereby decreasingcapacitance and thereby reducing electricity dissipation.

In [4], a evaluate of some current strategies to be had for clock gating is provided. Also a brand newa method that provides more immunity to the prevailing problems in available strategies is mentioned.

#### III. METHOD OF SOLUTION

Multi-bit Flip-Slump technique is to dispense with thetotal inverter number by sharing the inverters in theflip-flops. Information driven clock gating diminish redundantclock beats. Mix of Multi-bit Flip-Flopwith Information driven clock gating will increment thefurther control sparing. Xilinx programming device is utilized for actualizing this proposed framework. This paperstudies information driven clock gating, utilized for FFs at the entryway level, which is the most forceful possible. The clock flag driving a FF is incapacitated (gated)when the FFs state isn't liable to change in the following clock cycle [7]. Information driven gating is causing areaand control overheads that must be considered. In anattempt to lessen the overhead, it is proposed togroup a few FFs to be driven by the same clocksignal, produced by bring the empowering signs of the individual FFs. This may be that as it may, bring down thedisabling viability. It is in this manner useful togroup FFs whose exchanging exercises are highlycorrelated and infer a joint empowering signal. In arecent paper, a model for information driven gating isdeveloped in light of the flipping action of the constituent FFs [9].

The ideal fan-out of a clockgater yielding maximal power reserve funds is derivedbased on the normal flipping measurements of theindividual FFs, process innovation, and cell library inuse. By and large, the state changes of FFs in digitalsystems rely upon the information they process. Assessingthe adequacy of information driven clock gating requires, therefore, broad recreations and statisticalanalysis of the FFs' action. Another gathering of FFs for clock exchanging power lessening, called multi-bitFF (MBFF), has as of late been proposed in [10] and[11]. MBFF endeavors to physically combine FFs into asingle cell with the end goal that the inverters driving the clockpulse into its lord and slave hooks are sharedamong all FFs in a gathering. MBFF gathering is mainlydriven by the physical position vicinity of individual FFs, while gathering for information driven clockgating should consolidate flipping likeness withphysical position contemplations. While [9] replied the topic of what is the gathering size that amplifies control investment funds, this paper thinks about the inquiries of: 1)which FFs ought to be put in a gathering to maximize the control diminishment and 2) how to algorithmicallyderive those gatherings.

Information Driven Clock Gating Clock empowering signals are extremely surely knew atthe framework level and along these lines can viably be defined and catch the periods where useful squares and modules don't should be timed. Those are laterbeing naturally orchestrated into clock empowering signals at the entryway level. By and large,

(A High Impact Factor & UGC Approved Journal)

Website: <u>www.ijirset.com</u>

### Vol. 6, Issue 8, August 2017

clockenabling signals are physically included for each FF as a some portion of a plan approach. All things considered, when modules ata high and door level are timed, the state changes of their fundamental FFs rely upon the information beingprocessed. Note that the entiredynamic control devoured by a framework stems from the periods where modules' clock signals areenabled. In this manner, paying little respect to how relativelysmall this period is, evaluating the adequacy ofclock gating requires broad recreations and statistical investigation of FFs flipping movement, aspresented accordingly.

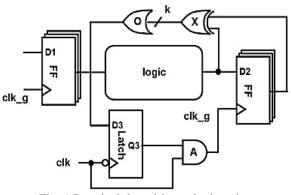

Fig. 1 Practical data-driven clock gating

Let the average toggling probability of a FF (alsocalled activity factor) be denoted by p (0 ). Under the worst-case assumption of independent FFtoggling, and assuming a uniform physical clock treestructure, it is shown in [9] that the number k ofjointly gated FFs for which the power savings are maximized is the solution of

$$(1-p)kln(1-p)(cFF+cW)+clatch/k2=0$$

.....(1)

Where cFF is the FFs clock input capacitance, cW is

the unit-size wire capacitance, and clatch is the latch

capacitance including the wire capacitance of its clkinput. Table I shows how the optimal k depends on p. Such a gating scheme has considerable timingimplications, which are discussed in [9]. We willreturn to those when discussing the implementation data-driven gating as a part of a complete designflow.

#### **Implementation and Integration Ina Design Flow:**

In the following, we describe the implementation of data-driven clock gating as a part of a standardbackend design flow. It consists of the followingsteps.

1) Estimating the FFs toggling probabilities involves running an extensive test benchrepresenting typical operation modes of the system to determine the size k of a gated FFgroup by solving (1).

2) Running the placement tool in hand to getpreliminary preferred locations of FFs in thelayout.

3) Employing a FFs grouping tool to implement model and algorithms presented, using the toggling correlation dataobtained in Step 1 and FF locations' dataobtained in Step 2. The outcome of this step isk-size FF sets (with manual overrides ifrequired), where the FFs in each set will bejointly clocked by a common gater.

4) Introducing the data-driven clock gating logicinto the hardware description (we use VerilogHDL). This is done automatically by a softwaretool, adding appropriate Verilog code to implement the logic described in Fig. 2. TheFFs are connected according to the groupingobtained in Step 3. A delicate practical questionis whether to introduce the gating

(A High Impact Factor & UGC Approved Journal)

Website: <u>www.ijirset.com</u>

### Vol. 6, Issue 8, August 2017

logic intoRTL or gate-level description. This depends ondesign methodology in use and its discussion isbeyond the scope of this paper. We have introduced the gating logic into the RTL description.

5) Re-running the test bench of Step 1 to verify the full identity of FFs' outputs before and after the introduction of gating logic. Although datadriven gating, by its very definition, should notchange the logic of signals, and hence FFstoggling should stay identical, a robust designflow must implement this step.

6) Ordinary backend flow completion. From thispoint, the backend design flow proceeds by applying ordinary place and route tools. This is followed by running clock-tree synthesis.

### IV. SIMULATION RESULTS

Fig. 2 Output Waveform of Clock GatedSynchronous FIFO

Fig. 3 Output Wave form of Synchronous FIFO Using MultibitFlipflopWith Data Driven Clock Gating.

(A High Impact Factor & UGC Approved Journal)

Website: <u>www.ijirset.com</u>

#### Vol. 6, Issue 8, August 2017

#### V. CONCLUSION

Normal clock gating is utilized forpower sparing. Be that as it may, clock gating still leaves largeramount of excess clock beats. Multibit flip-flopis likewise used to diminish control utilization. Utilizing of Multibit Flip-Slump strategy is to evacuate the totalinverter number by sharing the inverters in the flipflops. Blend of Multibit Flip-Tumble with Datadriven clock gating will expand the extra powersaving. Xilinx programming apparatus is utilized for implementingthis proposed framework. The mix of information drivengating with MBFF trying to yield additionalpower reserve funds.

#### REFERENCES

- [1] A. Kapoor et al., "Digital systems power management for high performance mixed signal platforms," IEEE Trans. Circuits Syst. I, Reg.Papers, vol. 61, no. 4, pp. 961–975, Apr. 2014.

- [2] H. Zhang, J. Rabaey, —Low-Swing Interconnect Interface Circuit"s,ISLPED-98: ACM/IEEE International Symposium on LowPower Electronics and Design, pp. 161-166, Monterey, CA, August 1998.

[3] J. Pangjun, S. S. Sapatnekar, —Clock Distribution using Multiple Voltages, ISLPED-99: ACM/IEEE International Symposium onLow-Power Electronics and Design, pp. 145-150, San Diego, CA, August 1999.

[4] JagritKathuria, M. Ayoubkhan, Arti Noor. "A R e v i e w o f C l o c k Ga t i n g Tech n iq u e s ", MIT International Journal of Electronics and CommunicationEngineering Vol. 1 No. 2 Aug 2011 pp 106-114.

[5] L. Benini, A. Bogliolo, and G. De Micheli, —A survey on design techniques for system-level dynamic power management, IEEETrans. Very Large Scale Integr. (VLSI) Syst., vol. 8, no. 3, pp. 299–316, Jun. 2000.

[6]. M.S.Hosny and W.Yuejian "Low powerclocking strategies in deepsubmicrontechnologies", Proc. IEEE Intll.Conf. Integr. Circuit DesignTechnol., pp.143 -146 2008

[7]. C. Chunhong, K. Changjun and S.Majid "Activity-sensitive clock treeconstruction for low power", Proc. Int.Symp.Low Power Electron. Design, pp.279 -2822002

[8]. G. Palumbo , F. Pappalardo and S.Sannella "Evaluation on power reductionapplying gated clock approach", Proc. IEEEISCAS 2002, vol. 44, pp.IV85 -IV88 2002

[9]. M. E. Hamid and C. H. Chen "A note to lowpower linear feedback shift register", IEEETrans. Circuits Syst. II, Analog Digit. SignalProcess., vol. 45, no. 9, pp.1304 -13071998

[10]. T. Lang, E. Musoll and J.Cortadella "Individual flip-flops with gatedclocks for low power datapaths", IEEETrans. Circuits Syst. II, Analog Digit. SignalProcess., vol. 44, no. 6, pp.507 -516 1997

[11]. M. Lowy "Parallel implementation of linearfeedback shift register for low powerapplications", IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., vol. 43, no.6, 1996.

[12] S.-H. Wang, Y.-Y.Liang, T.-Y.Kuo, and W.-K. Mak, "Power-driven flipflop merging and relocation," IEEE Trans. CAD Integr. Circuits Syst., vol. 31, no. 2, pp. 180–191, Feb. 2012.

[13] S-C. Lo, C-C. Hsu, and MP-H. Lin, "Power optimization for clocknetwork with clock gate cloning and flip-flop merging," in Proc. ACMInt. Symp. Phys. Design, 2014, pp. 77–84.

[14] S. Wimer, D. Gluzer, and U. Wimer, "Using well-solvable minimumcost exact covering for VLSI clock energy minimization," OperationsRes. Lett., vol. 42, no. 5, pp. 332–336, Jul. 2014.

[15] SpyGlass Power, accessed on 2016. [Online]. Available: http://www.atrenta.com/solutions/spyglass-family/spyglass-power.htm