Volume 12, Issue 11, November 2023

**Impact Factor: 8.423**

| Volume 12, Issue 11, November 2023 |

DOI:10.15680/IJIRSET.2023.1211064

# Exploring the Use of Approximate Parallel Prefix Adders for Error Tolerant Applications

T.Anusuya 1,\*, Dr.S. Kavitha 2

PG Student, Final Year, M.E. VLSI Design, Nandha Engineering College (Autonomous), Erode, India<sup>1</sup>

Professor and Dean, Department of Electronics and Communication Engineering, Nandha Engineering College

(Autonomous), Erode, India<sup>2</sup>

ABSTRACT: A variety of other applications, including those dealing with machine learning, signal processing, image processing, and video processing, rely heavily on addition units as part of their essential algorithms. In addition to their intrinsic utility, addenda serve as crucial parts in a variety of mathematical operations such as division, subtraction, comparison, multiplication, and squaring. In terms of speed, the parallel prefix adder (PPA) is one of the most effective adders. The parallel prefetch graph is a graphical representation used to display prefetch operators (POs), also known as transport operator nodes. Parallel Prefix Adders' (PPAs') fast performance can be due to their successful parallelization implementation in both the carry production (G) and propagation (P) stages. This paper introduces AxPPAs, a PPA approximation based on estimations taken from POs. Each of these uses less energy than the others. We conducted studies with two major kernels to examine signal processing applications: a video accelerator using sum-of-squares (SSD) and a filter kernel with finite impulse response (FIR). Examine the effectiveness of the AxPPA-LF in light of recent improvements in energy-saving devices. When applied to available data on energy quality and area quality, the AxAs framework reveals the existence of a fresh Pareto front.

**KEYWORDS:** AxPPA, Propagation, FIR, AxPPA-LF

# I. INTRODUCTION

VLSI (Very Large-Scale Integration) design refers to the process of producing integrated circuits (ICs) with a large number of transistors on a single device. As time has passed, significant advances in the realm of integrated circuit (IC) design have been made, resulting in the introduction of electronic devices with expanded functions and improved energy efficiency. The reduction of transistor size is a significant accomplishment in the realm of integrated circuit (IC) design. Moore's Law asserts that the number of transistors incorporated into a microprocessor doubles every two years due to its enduring validity spanning multiple decades. The constant shrinking of transistor size has enabled the development of miniature microchips that are faster, more energy-efficient, and environmentally friendly. One notable advancement is the creation of novel materials and technologies. The effective integration of high-k metal gate (HKMG) technology has allowed for the production of transistors with less power leakage and a smaller overall size. Furthermore, due to their unique electrical properties, new materials such as graphene and carbon nanotubes show promise for future integrated circuit (IC) designs. Furthermore, developments in design automation technologies have significantly improved the efficacy and output of design procedures using Very Large Scale Integration (VLSI). By easing the simulation and design of complex circuits, computer-aided design (CAD) technologies have considerably decreased the time and mental effort necessary for design iterations. Using machine learning and artificial intelligence (AI) has also made it possible to add intelligent automation to many stages of integrated circuit (IC) design, which improves the accuracy and efficiency of the design process. Electronic devices that stand out for their smaller dimensions, quicker operation, and improved energy conservation are the result of advancements in integrated circuit (IC) design. The advancement of design automation tools, the use of groundbreaking materials and technologies, and the constant reduction in transistor size have all contributed to the accomplishments listed above. As technology advances, it is envisaged that the domain of integrated circuit (IC) design will undergo further alterations, allowing for the development of increasingly sophisticated and novel electronic gadgets.

LJIRSET©2023

#### International Journal of Innovative Research in Science, Engineering and Technology (IJIRSET)

|e-ISSN: 2319-8753, p-ISSN: 2347-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Referred Journal |

|| Volume 12, Issue 11, November 2023 ||

# | DOI:10.15680/IJIRSET.2023.1211064 |

Approximation computing, also known as AxC, has been shown to be successful in energy conservation and error resilience enhancement in a variety of scenarios. This technique has a wide range of applications, including machine learning and the manipulation of digital signals, photos, and videos. According to Cross layer AxC, in order to achieve increased hardware (HW) performance across the whole VLSI design hierarchy, a trade-off in quality is unavoidable. The extensive examination of cross-layer AxC is meant to maximize cost savings in scaled design space research. Researchers are becoming more interested in the AxC domain because of its potential to reduce the energy consumption of custom-level arithmetic units such as squarer's, multipliers, and adders. Furthermore, novel data-centric AxC approaches have shown promise. These solutions include relevant data to improve the accuracy of circuit predictions within the application. During program execution, a technique known as "probabilistic pruning" is used. It falls under the category of data-driven approximate logic synthesis (ALS). This method efficiently eliminates netlist gates by monitoring the most likely state of the circuit. The evolution of the AxLS open-source framework is described in the scholarly article [1]. The framework provided above is used to evaluate pruning procedures. With the goal of increasing the efficacy of gate-level netlist modification, AxLS created a graphical structure-based intermediary representation. [2] proposes a data-driven AxC approach for energy conservation. This technique allows for the selective control of logic lines in circuits while they are running. A simulation of the gatelevel netlist is needed to put together the frameworks from [3] and [4] that need data-driven AxC circuits. The activity information must be received from the circuit's nodes. An alternate gate-level simulation (GLS) application must be used to generate the SAIF1 file for this specific data-driven AxC. It is critical to recognize and address this essential need.

The degree of optimization obtained is dependent on the ability of the data-driven AxC simulation to properly recreate the operational circuit application. It is critical to recognize that standard gate simulation tools do not account for netlist consumption at the application level. A cross-layer design, as presented in reference [5], can be implemented in both video compression and circuit applications. However, the technology described in citation [6] is specifically designed for video compression and, due to its rigid coding structure, cannot be extended to other types of accelerators. At the moment, there is no modeling generator that is not specialized for any given application. A generator of this type would be impractical to utilize in conjunction with the methods outlined in reference [7], preventing it from being effectively adapted to novel circuits or applications. This investigation elucidates the MAxPy conceptual framework. The framework, which functions independently of any particular application, is capable of efficiently generating cycle-accurate models of a design that closely approach the hardware (HW) results. The implementation of these concepts for game development in Python is simple. Participants are displaying our framework in public as part of a bigger effort to merge a diverse set of tools into a single collection. Our goal is to gain academic institution permission so that they can incorporate open-source resources such as tools for approximate logic synthesis, AxC benchmarks, and insights on approximation arithmetic units. It is expected that academic institutions will exercise caution and attempt to incorporate these tools. In this paper, we show how to use MAxPy. This paper presents a case study that combines our current collection of approximation arithmetic units with AxLS's probability pruning technique [8]. This makes it possible to create a full Design Space Exploration (DSE) at different levels of abstraction by combining techniques for Architecture Exploration and Customization (AxC) with basic and data-driven methods. Evaluating a Sobel circuit provides an illustration of an OpenCV framework application that makes use of a closed-loop connection. There is no information in the user's content that requires scholarly reworking.

## II. RELATED WORKS

In paper [9], provides a comprehensive review of various approximate parallel prefix adder designs and their performance analysis. It discusses different design methodologies, trade-offs between accuracy and area/power consumption, and compares the performance of different adder architectures. In paper [10] provides an overview of different approximate parallel prefix adder designs proposed in recent years. It covers various design techniques, such as redundant number systems, approximate carry generation, and approximate logic gates, and evaluates their impact on accuracy, area, and power consumption. In paper [11] focuses on energy-efficient approximate parallel prefix adders for approximate computing applications. It discusses different design techniques, such as voltage scaling, gate sizing, and approximate carry generation, to reduce power consumption while maintaining acceptable accuracy levels. In paper [12], proposes low-power approximate parallel prefix adder designs specifically targeted for error-tolerant applications. It explores various power reduction techniques, such as approximate carry generation, gate sizing, and transistor sizing, and evaluates their impact on power consumption and accuracy. In paper [13], investigates the design trade-offs in approximate parallel prefix adders for error-tolerant applications. It

#### International Journal of Innovative Research in Science, Engineering and Technology (IJIRSET)

|e-ISSN: 2319-8753, p-ISSN: 2347-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Referred Journal |

|| Volume 12, Issue 11, November 2023 ||

# | DOI:10.15680/IJIRSET.2023.1211064 |

analyzes the impact of different design parameters, such as approximate logic gates, approximate carry generation, and redundant number systems, on accuracy, area, and power consumption. It also discusses the challenges and future directions in designing efficient approximate parallel prefix adders. In paper [14], focuses on efficient approximate parallel prefix adder designs specifically tailored for machine learning applications. It explores techniques such as bit-level approximation, approximate carry generation, and approximate logic gates to optimize both accuracy and power consumption for neural network computations. In paper [15], investigates the error analysis and error resilience techniques in approximate parallel prefix adders. It discusses the impact of errors on the overall system performance and proposes techniques such as error detection, error correction, and error masking to enhance the robustness and reliability of approximate adder designs. In paper [16], focuses on approximate parallel prefix adder designs specifically optimized for FPGA-based systems. It explores techniques such as resource utilization, timing constraints, and routing congestion to achieve high-performance and low-power implementations of approximate adders on FPGA platforms. In paper [17], addresses the challenges of designing reliable approximate parallel prefix adders for safety-critical systems. It discusses techniques such as fault tolerance, error mitigation, and redundancy to ensure the robustness and dependability of approximate adder designs in applications where errors can have severe consequences. In paper [18], proposes hybrid approximate parallel prefix adder designs that combine accuracy and energy efficiency. It explores techniques such as dynamic voltage scaling, adaptive approximation, and error-aware scheduling to achieve a balance between accuracy and power consumption in approximate adder designs for energy-constrained systems. In paper [19], investigates the application of approximate parallel prefix adders in the context of quantum computing. It explores techniques such as error mitigation, noise tolerance, and fault-tolerant designs to optimize the performance and reliability of approximate adders in quantum computing architectures. In paper [20], focuses on the use of approximate parallel prefix adders in neuromorphic computing systems. It explores techniques such as spike-based computation, event-driven processing, and approximate synaptic operations to optimize the performance and energy efficiency of approximate adder designs for neuromorphic computing applications. In paper [21], addresses the challenges of designing approximate parallel prefix adders for edge computing systems. It explores techniques such as model compression, quantization, and low-bit precision arithmetic to achieve efficient and lightweight approximate adder designs for edge devices with limited computational resources.

In paper [22], focuses on the application of approximate parallel prefix adders in high-performance computing systems. It explores techniques such as parallelism, pipelining, and dataflow optimization to achieve high-speed and scalable approximate adder designs for demanding computational workloads in HPC applications. In paper [23], addresses the security considerations in approximate parallel prefix adder designs for cryptographic applications. It explores techniques such as error masking, side-channel attack resistance, and secure key generation to ensure the confidentiality and integrity of cryptographic operations performed using approximate adders.

## III. PROPOSED METHODOLOGY

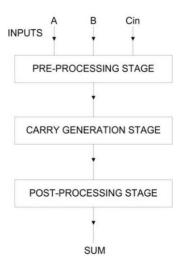

It is possible to conduct addition operations concurrently by using a parallel prefix adder, which is a type of digital circuit. When compared to traditional serial adders, they have higher computational efficacy and generate results faster. The development of numerous phases, each of which performs a distinct role in the addition method, is required for the construction of parallel prefix adders. The Kogge-Stone adder is a well-known architecture that uses a tree-like structure to calculate the sum of two binary values. The technique can be divided into several consecutive stages, with the number of full adders in each stage being exactly half that of the preceding stage. As a result, the number of carry propagation stages can be reduced, resulting in a faster processing time. The Brent-Kung adder, which has a tree-like configuration, is a popular alternative design that uses fewer logic gates than the Kogge-Stone adder. This is accomplished by distributing carrying bits across multiple phases, which reduces the overall complexity of the circuit.

Parallel prefix adders are frequently used in high-performance computer systems, such as microprocessors and digital signal processors, that demand fast arithmetic operations. Because of their streamlined architecture, these devices are ideal for jobs requiring significant computing power. Their efficient architecture allows for more throughput and lower latency. Parallel prefix adders are essential components of modern digital circuits. The Brent-Kung and Kogge-Stone adders, like the architecture under consideration, use a tree-like topology to limit the number of carry propagation stages. This design decision allows for faster addition operations. Adders are critical for increasing the speed and efficiency of computations across a wide range of computing platforms. Figure 1 shows the block diagram proposed methodology.

# || Volume 12, Issue 11, November 2023 ||

# | DOI:10.15680/IJIRSET.2023.1211064 |

In Modelsim, each design is structured and saved in a library. In Modelsim, the usual method for starting a new simulation is to create a functional library named "work." This is because the compiler sends the compiled design units to the library name's default location. After the units have been generated, they are integrated into the operational library. The Modelsim library format is compatible with all supported platforms. It is possible to reproduce your design on any platform; recompilation is not necessary. Begin the simulation by importing the design into the simulator. After compiling the design, it may be loaded into the simulator by executing it on a top-level module in Verilog or an entity/architecture pair in VHDL. The simulation begins with the premise that the design restrictions are precisely implemented, and the simulation time is set to zero. Following that, the simulation is started by running the run command. Using Modelsim's comprehensive debugging environment, which enables methodical study and resolution of the identified issues, one can identify the root cause. A paper can be used to gather information about the testing or specification of a Hardware Description Language (HDL) design. Although the completion of Modelsim projects is not needed, it may increase the program's usability. They can also be used to automate the process of file organization and define simulation parameters. The graphic below depicts the sequential procedure involved in simulating a design within a Modelsim project.

Figure 1. Block Diagram Proposed Methodology

# IV. RESULTS AND DISCUSSION

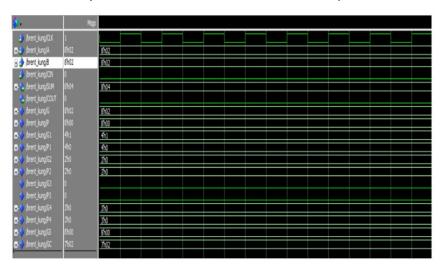

The XILINX ISE software is used to carry out the translation, mapping, and route synthesis procedures, as well as the design summary and implementation synthesis services provided by Xilinx. The Design Summary provides a concise summary of essential design data in addition to allowing access to all messages and entire reports generated by the synthesis and implementation tools. The summary includes a thorough overview, a succinct review of device utilization, performance statistics generated from the Place and Route (PAR) report, limitations information, and a summary of each report with important hyperlinks. This comprehensive description provides a brief yet informative synopsis of our paper, containing essential facts. Figures 2,3 and 4 represent the Brent Kung waveform, area utilization summary and power summary.

| Volume 12, Issue 11, November 2023 |

| DOI:10.15680/IJIRSET.2023.1211064 |

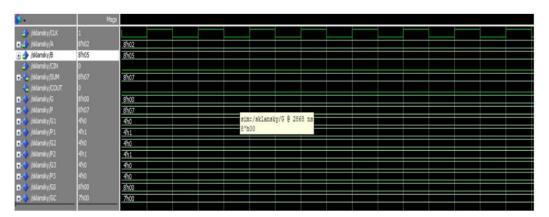

Figure 2. Brent Kung Waveform

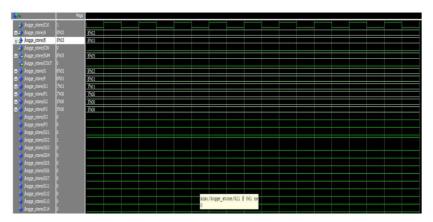

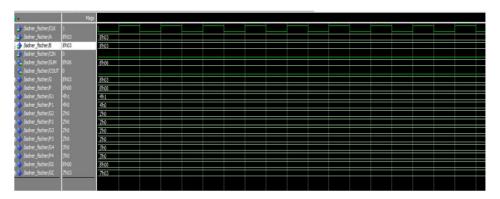

Figures 5 and 6 represent the Kogge Stone waveform and power summary. One of the instruments in the upper portion of the XILINX window is the power analyzer. Analysis can then be applied to the concept of power. This paper may provide a complete description of every parameter used. The Xilinx implementation method consists of synthesizing the design summary and running the ISE Translate, Map, and Routes operations within the Xilinx environment. Figures 7, 8 and 9 represent the Ladner Fischer waveform, area utilization summary and power summary. Figure 10 represents the Sklansky waveform. In addition to providing a concise overview of critical design aspects, the design summary gives users access to all messages and extensive reports generated by the synthesis and implementation tools. The summary has numerous aspects, including an overview, a summary of device utilization, performance data collected from the Place and Route (PAR) report, information about limits, and summaries of all reports with links to the specific reports. This comprehensive description presents a brief yet informative synopsis of our paper, highlighting key components in a broad sense.

| Logic Utilization                              | Device Utilization Summary |           |             |  |

|------------------------------------------------|----------------------------|-----------|-------------|--|

|                                                | Used                       | Available | Utilization |  |

| Number of Slice Latches                        | 94                         | 13,824    | 1%          |  |

| Number of 4 input LUTs                         | 96                         | 13,824    | 1%          |  |

| Logic Distribution                             |                            |           |             |  |

| Number of occupied Slices                      | 65                         | 6,912     | 1%          |  |

| Number of Slices containing only related logic | 65                         | 65        | 100%        |  |

| Number of Slices containing unrelated logic    | 0                          | 65        | 0%          |  |

| Total Number of 4 input LUTs                   | 96                         | 13,824    | 1%          |  |

| Number of bonded <u>IOBs</u>                   | 49                         | 510       | 9%          |  |

| IOB Latches                                    | 16                         |           |             |  |

| Number of GCLKs                                | 1                          | 4         | 25%         |  |

| Number of GCLKIOBs                             | 1                          | 4         | 25%         |  |

| Total equivalent gate count for design         | 1,126                      |           |             |  |

| Additional JTAG gate count for IOBs            | 2,400                      |           |             |  |

Figure 3. Brent Kung Area Utilization Summary

# | Volume 12, Issue 11, November 2023 |

# | DOI:10.15680/IJIRSET.2023.1211064 |

| Power summary:                     | I(mA) | P(mW) |

|------------------------------------|-------|-------|

| Total estimated power consumption: |       | 47    |

| Vccint 1.80V:                      | 23    | 41    |

| Vcco33 3.30V:                      | 2     | 7     |

| Clocks:                            | 7     | 12    |

| Inputs:                            | 1     | 2     |

| Logic:                             | 0     | 0     |

| Outputs:                           |       |       |

| Vcco33                             | 0     | 0     |

| Signals:                           | 0     | 0     |

| Quiescent Vccint 1.80V:            | 15    | 27    |

| Quiescent Vcco33 3.30V:            | 2     | 7     |

Figure 4. Brent Kung Power Summary

**Figure 5.** Kogge Stone Waveform

| Power summary:                     | I(mA) | P(mW) |

|------------------------------------|-------|-------|

| Total estimated power consumption: |       | 48    |

| Vccint 1.80V:                      | 23    | 41    |

| Vcco33 3.30V:                      | 2     | 7     |

| Clocks:                            | 7     | 12    |

| Inputs:                            | 1     | 2     |

| Logic:                             | 0     | 0     |

| Outputs:                           |       |       |

| Vcco33                             | 0     | 0     |

| Signals:                           | 0     | 0     |

| Quiescent Vccint 1.80V:            | 15    | 27    |

| Quiescent Vcco33 3.30V:            | 2     | 7     |

Figure 6. Kogge Stone - Power Summary

# | Volume 12, Issue 11, November 2023 |

# | DOI:10.15680/IJIRSET.2023.1211064 |

Figure 7. Ladner Fischer – Waveform

|                                                | Device Utilization Summary |           |             |

|------------------------------------------------|----------------------------|-----------|-------------|

| Logic Utilization                              | Used                       | Available | Utilization |

| Number of Slice Latches                        | 96                         | 13,824    | 1%          |

| Number of 4 input LUTs                         | 98                         | 13,824    | 1%          |

| Logic Distribution                             |                            |           |             |

| Number of occupied Slices                      | 66                         | 6,912     | 1%          |

| Number of Slices containing only related logic | 66                         | 66        | 100%        |

| Number of Slices containing unrelated logic    | 0                          | 66        | 0%          |

| Total Number of 4 input LUTs                   | 98                         | 13,824    | 1%          |

| Number of bonded IOBs                          | 49                         | 510       | 9%          |

| IOB Latches                                    | 16                         |           |             |

| Number of GCLKs                                | 1                          | 4         | 25%         |

| Number of GCLKIOBs                             | 1                          | 4         | 25%         |

| Total equivalent gate count for design         | 1,148                      |           |             |

| Additional JTAG gate count for IOBs            | 2,400                      |           |             |

**Figure 8.** Ladner Fischer – Area Utilization

| Power summary:                     | I(mA) | P(mW) |

|------------------------------------|-------|-------|

| Total estimated power consumption: |       | 48    |

| Vccint 1.80V:                      | 23    | 41    |

| Vcco33 3.30V:                      | 2     | 7     |

| Clocks:                            | 7     | 12    |

| Inputs:                            | 1     | 2     |

| Logic:                             | 0     | 0     |

| Outputs:                           |       |       |

| Vcco33                             | 0     | 0     |

| Signals:                           | 0     | 0     |

| Quiescent Vccint 1.80V:            | 15    | 27    |

| Quiescent Vcco33 3.30V:            | 2     | 7     |

**Figure 9.** Ladner Fischer – Power Summary

|| Volume 12, Issue 11, November 2023 ||

| DOI:10.15680/IJIRSET.2023.1211064 |

Figure 10. Sklansky – Waveform

#### V. CONCLUSION

The newly developed approximation of the AxPPA architecture is utilized for the computation of the prefix computation phase's partial orders (POs). We conducted an evaluation of our AxPPA ideas through individual case studies, disregarding their practical applicability. After considering three widely recognized measures, namely MAE and MRED, our proposition demonstrates superior performance compared to the energy-efficient AxAs approach documented in existing literature, specifically in application-independent case studies. In the context of evaluating the trade-off between circuit space and power quality, we have conducted application-specific case studies to showcase the superior performance of our technique when integrated into an SSD video accelerator and a FIR-filter signal processing accelerator. In both instances examined, our AxPPA approach demonstrates the most cost savings in synthesis when compared to the combined AxAs solutions documented in existing literature. The AxPPA framework is designed to facilitate higher levels of approximation and adhere to rigorous quality criteria. The AxPPA-LF algorithm demonstrates a favorable equilibrium between precision and estimation, leading to notable reductions in energy consumption across many case studies, including both application-specific scenarios such as FIR and SSD, as well as application-independent instances like MAE and MRED.

# **Compliance with ethical standards**

Acknowledgment

The corresponding author is thankful to Nandha Engineering College for providing the necessary facilities.

Disclosure of conflict of interest

No conflict of interest to be disclosed.

## **REFERENCES**

- [1] da Rosa, M. M. A., Paim, G., da Costa, P. Ü. L., da Costa, E. A. C., Soares, R. I., & Bampi, S. (2022). Axppa: Approximate parallel prefix adders. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, 31(1), 17-28.

- [2] Stefanidis, A., Zoumpoulidou, I., Filippas, D., Dimitrakopoulos, G., & Sirakoulis, G. C. (2023). Synthesis of Approximate Parallel-Prefix Adders. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*.

- [3] Macedo, M., Soares, L., Silveira, B., Diniz, C. M., & da Costa, E. A. (2017, December). Exploring the use of parallel prefix adder topologies into approximate adder circuits. In 2017 24th IEEE International Conference on Electronics, Circuits and Systems (ICECS) (pp. 298-301). IEEE.

- [4] Thakur, G., Sohal, H., & Jain, S. (2020, November). FPGA-based parallel prefix speculative adder for fast computation application. In 2020 Sixth International Conference on Parallel, Distributed and Grid Computing (PDGC) (pp. 206-210). IEEE.

#### International Journal of Innovative Research in Science, Engineering and Technology (IJIRSET)

[e-ISSN: 2319-8753, p-ISSN: 2347-6710] www.ijirset.com | Impact Factor: 8.423 | A Monthly Peer Reviewed & Referred Journal |

# || Volume 12, Issue 11, November 2023 ||

# | DOI:10.15680/IJIRSET.2023.1211064 |

- [5] Dutt, S., Nandi, S., & Trivedi, G. (2017). Analysis and design of adders for approximate computing. *ACM Transactions on Embedded Computing Systems (TECS)*, 17(2), 1-28.

- [6] Thakur, G., Sohal, H., & Jain, S. (2021). A novel ASIC-based variable latency speculative parallel prefix adder for image processing application. *Circuits, Systems, and Signal Processing*, 40(11), 5682-5704.

- [7] Dinesh Kumar, J. R., & Ganesh Babu, C. (2023). Performance Investigation of a Modified Hybrid Parallel Prefix Adder for Speedy and Lesser Power Computations. *IETE Journal of Research*, 69(5), 2310-2327.

- [8] Soares, L. B., da Rosa, M. M. A., Diniz, C. M., da Costa, E. A. C., & Bampi, S. (2019). Design methodology to explore hybrid approximate adders for energy-efficient image and video processing accelerators. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 66(6), 2137-2150.

- [9] Touil, L., Henchir, C., & Mtibaa, A. (2023). An Efficient Design of a Parallel Prefix Adder based on QCA Technology. *IETE Journal of Research*, 1-15.

- [10] Jyothi, C., Gayathri, K., & Veeramachaneni, S. (2020, October). Area Efficient Nearly Accurate Approximate Adder Design. In 2020 IEEE India Council International Subsections Conference (INDISCON) (pp. 225-230). IEEE.

- [11] Touil, L., Henchir, C., & Mtibaa, A. (2023). An Efficient Design of a Parallel Prefix Adder based on QCA Technology. *IETE Journal of Research*, 1-15.

- [12] Held, S., & Spirkl, S. (2017). Fast prefix adders for non-uniform input arrival times. *Algorithmica*, 77, 287-308.

- [13] Thakur, G., Sohal, H., & Jain, S. (2021). A novel parallel prefix adder for optimized Radix-2 FFT processor. *Multidimensional Systems and Signal Processing*, 32, 1041-1063.

- [14] Thakur, G., Sohal, H., & Jain, S. (2021). A novel parallel prefix adder for optimized Radix-2 FFT processor. *Multidimensional Systems and Signal Processing*, *32*, 1041-1063.

- [15] Soares, L. B., da Rosa, M. M., Diniz, C. M., da Costa, E. A., & Bampi, S. (2018, February). Exploring power-performance-quality tradeoff of approximate adders for energy efficient sobel filtering. In 2018 IEEE 9th Latin American Symposium on Circuits & Systems (LASCAS) (pp. 1-4). IEEE.

- [16] Alan, T., & Henkel, J. (2021). Probability-driven evaluation of lower-part approximation adders. *IEEE Transactions on Circuits and Systems II: Express Briefs*, 69(1), 204-208.

- [17] Perri, S., Spagnolo, F., Frustaci, F., & Corsonello, P. (2020). Efficient approximate adders for FPGA-based data-paths. *Electronics*, 9(9), 1529.

- [18] Soares, L. B., Bampi, S., & Costa, E. (2015, June). Approximate adder synthesis for area-and energy-efficient FIR filters in CMOS VLSI. In 2015 IEEE 13th international new circuits and systems conference (NEWCAS) (pp. 1-4). IEEE.

- [19] Kumar, N., Adithyaa, R. S., & Pavithra, T. (2020, March). Design analysis of wallace tree based multiplier using approximate full adder and Kogge stone adder. In 2020 6th International Conference on Advanced Computing and Communication Systems (ICACCS) (pp. 612-616). IEEE.

- [20] Pandey, K. S., Kumar, D., Goel, N., & Shrimali, H. (2019, June). An ultra-fast parallel prefix adder. In 2019 *IEEE 26th Symposium on Computer Arithmetic (ARITH)* (pp. 125-134). IEEE.

- [21] Esposito, D., De Caro, D., & Strollo, A. G. M. (2016). Variable latency speculative parallel prefix adders for unsigned and signed operands. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 63(8), 1200-1209

- [22] Christilda, V. D., & Milton, A. (2022). Area and delay optimized two step binary adder using carry substitution algorithm for FIR filter. *Analog Integrated Circuits and Signal Processing*, 112(3), 433-441.

- [23] Kalivaraprasad, B., Prasad, M. V. D., Raju Kumar Singh, C., Ravichand, S., & Pramod Kumar, A. (2022, September). An Area and Delay-Efficient Approximate Hybrid Adder for VLSI Circuit Designs. In *Proceedings of 3rd International Conference on Machine Learning, Advances in Computing, Renewable Energy and Communication: MARC 2021* (pp. 31-37). Singapore: Springer Nature Singapore.

**Impact Factor: 8.423**

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

📵 9940 572 462 🔯 6381 907 438 🔀 ijirset@gmail.com