e-ISSN: 2319-8753 | p-ISSN: 2347-6710

DIA

International Journal of Innovative Research in SCIENCE | ENGINEERING | TECHNOLOGY

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

Volume 13, Issue 5, May 2024

INTERNATIONAL STANDARD SERIAL NUMBER INDIA

### Impact Factor: 8.423

9940 572 462

6381 907 438

$\bigcirc$

🖂 ijirset@gmail.com

よう 🕸 IJIRSET

|e-ISSN: 2319-8753, p-ISSN: 2347-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Refereed Journal |

|| Volume 13, Issue 5, May 2024 ||

DOI:10.15680/IJIRSET.2024.1305569

## Efficient SoC Integration with High Performance and Minimal Leakage Using Multi-Vt Technology

#### Miloni Ganatra

Assistant Professor, Department of Electronic & Communication Engineering, Indus University, Ahmadabad,

Gujarat, India

**ABSTARCT:** This paper proposes a total power and delay optimization flow at synthesis stage and CTS (Clock Tree Synthesis) stage of VLSI Design flow. Multiple Vt design approach is required for reducing leakage current. In this Paper, two combinations of Vt are used: 1. High Vt and 2. Low Vt for the same logic function. The third type is nominal Vt is optional in this flow, Implementation flows use different approaches to use mixture of different flavors of cells in the design to make trade-off between leakage and performance targets. In this paper RTL synthesis and logic optimization will be performed using LVT cells to optimize timing with high speed cells for meeting the timing target. Then once the delay is met, the leakage power optimization will be implemented with target slack of zero and leakage power optimization will be done with only HVT cells.

KEYWORDS: Synthesis, skew, Insertion delay, Latency, Clock Tree Synthesis (CTS), System on Chip (SoC), Slack

#### I. INTRODUCTION

When a CMOS cell output is stable in SoC, ideally only the PMOS section or the NMOS section is conductingand in principle no current flows from supply to ground. However, a small amount of current does leak through the non-conducting section. One effect of advanced technologies is that leakage current is becoming Significant, and might even be a major contributor to power consumption. Silicon foundries are now providing multiple-threshold-voltage (multi-Vt) libraries, which allow designers to reduce power consumption due to leakage current.

As the design size is shrinking to the ultra-deep sub microns and density is increasing to millions of gates in a system on chip, large power dissipation in the chip due to sub-threshold leakage is becoming uncontrollable in the practical world. It is taking more importance as it is becoming dominant component for the overall power in the chip. There have been many researches going on recently to extend the battery life as the hand held mobile devices are densely packed with multiple functionalities.

The delay of logical gates increases with the increase in threshold voltage (High Vt), whereas the static power decreases with the increase in threshold voltage. This can be represented by a simple gate delay equation:

#### Delay, Td = (CLVdd) / (Vdd - Vt)a

In the equation, Td represents the propagation delay, CL is the load capacitance, Vdd is the supply voltage and Vt is the threshold voltage for the transistor. a is the coefficient and represents the effect due to shortening of the device channel length (scaling down technology).

The leakage current of a MOS transistor can be approximated as follows:

$I_{leak} = Ae^{q(Vgs - Vth)/nkT}(1 - e^{-qVds/kT})$ where, A =  $\mu oC_{ox}(W_{eff}/L_{eff})(kT/q)^2 e1.8$

Cox = Gate oxide capacitance per unit area Vth = Threshold voltage

|e-ISSN: 2319-8753, p-ISSN: 2347-6710| <u>www.ijirset.com</u> | Impact Factor: 8.423| A Monthly Peer Reviewed & Refereed Journal |

#### || Volume 13, Issue 5, May 2024 ||

#### | DOI:10.15680/IJIRSET.2024.1305569 |

Leakage exponentially varies with threshold voltage.

Lower-Vt devices are needed to cater theperformance targets Engineers to make right trade-off between leakage power Vs performance targets.

All the above factors that are being discussed are needed to be considered carefully at each level of design abstraction for the deep sub-micron SoC designs. In this paper, I have propose total power and delay optimization flow at synthesis stage and CTS stage. At Synthesis stage I have proposed flow using multivtlibrary (Swapping of cells) which uses HVT(High threshold voltage),LVT(Low Threshold Voltage) and RVT(Regular Threshold voltage) cells. To build a clock tree I have proposed a flow using multivt library which includes pure HVT, pure RVT and pure LVT cells.

#### II. MULTIPLE VT LIBRARIES FOR LEAKAGE AND SPEED OPTIMIZATION

Multiple Vt design approach is required for reducing leakage current. Multiple Vt design is one of the important methods to design the deep submicron circuits in the power constrained era.Multi-Vt Library consists of different standard cells with different threshold devices.

- HVT cells High Threshold Voltage cells

- RVT cells Regular Threshold Voltage cells

- LVT cells Low Threshold Voltage cells

#### A. Multi-Vt Library Profiling

$I_{dsat}$  and  $I_{off}$  values of different threshold voltage transistors to be studied to understand the impact of leakage values of different flavors of

cells.Ioff values are indicators of leakage numbers and they varied as following:

$\begin{array}{l} HVT-1X\\ NVT-\sim\!\!20X\\ LVT-\sim\!\!50X\\ I_{dsat} \mbox{ values are the indicators of device performance.} \end{array}$

Sequential cells shown comparatively less variation than combinational cells but sequential cells contributed maximum leakage due to large number of devices. Selective use of NVT/LVT cells reduces leakage power while still meeting the same performance targets

In this flow, two combinations of Vt are used: 1. High Vt and 2. Low Vt for the same logic function. The third type is nominal Vt is optional in this flow. This is the minimum requirement in the technology library in order to pursue the leakage power optimization. No other changes in the design procedures are required as the technology mapping handles them in order to utilize the multiple Vt technology.

Combinations of high Vt and low Vt can be used to characterize the complex Vt cells in the library apart from just high Vt and just low Vt cells. The library size would be reasonably larger in this kind of characterized libraries. One more important thing to note is that the constant leakagepower in the library would slowly go away as the constant models are not accurate for 90 nm and below.

#### B. Design Flow

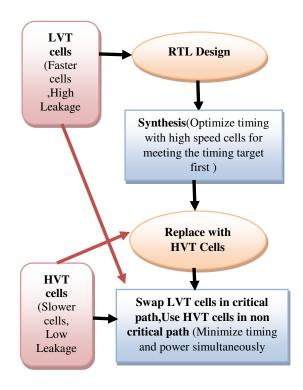

Implementation flows use different approaches to usemixture of different flavors ofcells in the design tomake trade-off between leakage and performancetargets. Here in this design flow (Fig. 1)shows that ,Once the data is available ,RTL synthesis and logic optimization will be performed using LVT (low threshold voltage cells) to optimize timing with high speed cells for meeting the timing target first because LVT cell has less delay but it has more leakage power . Then once the delay is met, the leakage power optimization will be implemented with target slack of zero and leakage power optimization will be done with only HVT cells (which has low leakage power but it has more delay). So, it is necessary to swap HVT Cells with LVT cells. The path which is timing critical in that path only LVT cells are used so it reduces the delay.

L C A

|e-ISSN: 2319-8753, p-ISSN: 2347-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Refereed Journal |

|| Volume 13, Issue 5, May 2024 ||

DOI:10.15680/IJIRSET.2024.1305569

Fig 1. Shows the design flow for swapping of LVTto HVTto LVT

C. Normalized delay and leakage current for a cell with different threshold voltages in 90nm Technology:

#### TABLE 1:

Normalized delay and leakage current for a cell with different threshold voltages in 90 nm Technology

| Cell             | HVT      | RVT      | LVT      |

|------------------|----------|----------|----------|

| Delay            | 663.6 ps | 463.3 ps | 374.9 ps |

| Leakage<br>Power | 1.7 nW   | 9.2 nW   | 23.8 nW  |

This Table 1 introduces the delay and leakage power for 90 nm technology for HVT, RVT, LVTcells it shows that delay of HVT cell is maximum and leakage power of HVT cells are minimum compared to another cells and delay of LVT cell is minimum and leakage power of LVT cell is maximum.

III. DESIGN EXPERIMENTS WITH MULTI-VT LIBRARIES

A.Design experiments with multi-Vt libraries at Synthesis stage

• **Synthesis**: Translation + Mapping + Optimization

|e-ISSN: 2319-8753, p-ISSN: 2347-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Refereed Journal |

|| Volume 13, Issue 5, May 2024 ||

#### | DOI:10.15680/IJIRSET.2024.1305569 |

• **Translation:** It is Process that generates a gate-level netlist for an IC design that has been defined using a Hardware Description Language (HDL)

• **Mapping:** It maps to particular technology library

• **Optimization:** It is Step in the synthesis process that attempts to implement a combination of library cells that best meet the functional, timing, and area requirements of the design

Table 2 shows the experiment done at synthesis stage using multivt library.

This table 2 shows the results of gate count, slack and leakage power using pure HVT, pure LVT and pure RVT and using all three cells at synthesis stage

From this table 2, Three Vt's add one more dimension to performance/power optimization, Leakage power can be saved, Silicon area is also improved. So, at synthesis stage best option is to use HVT and LVT cells, because using that we can meet the timing, slack is positive and leakage power is also controlled. So best way is to use the swapping of HVT and LVT cells (Use HVT cells in timing non critical path and use LVT cells in timing critical path. This Table2is the results from the multivt design flow.

#### TABLE II

#### Design experiments with multi-VT libraries at Synthesis stage

| Cell             | Pure HVT<br>cells | Pure RVT<br>cells | Pure LVT<br>cells | LVT an | nd HVT c | ells  | LVT,RV | VT and H | VT cells |

|------------------|-------------------|-------------------|-------------------|--------|----------|-------|--------|----------|----------|

| Gates            | 99197             | 111617            | 100089            | LVT    | RVT      | HVT   | LVT    | RVT      | HVT      |

|                  |                   |                   |                   | 52889  |          | 58617 | 44569  | 39121    | 49516    |

| Gate Count       | 99197             | 111617            | 100089            |        | 1        |       |        |          |          |

| Slack            | -267ps            | -100ps            | >0ps              | 0ps    |          |       | 0ps    |          |          |

| Leakage<br>Power | 456uw             | 561uw             | 768uw             | 296uw  |          |       | 321uw  |          |          |

B.Design experiments with different threshold voltage cells at CTS Stage (Clock Tree Building).

CTS develop the interconnect that connect the system clock to all the cells in the chip. Goals of CTS:

- Minimizing Clock skew

- Minimizing Insertion delay

- Skew is the difference in arrival of clock at two consecutive pins of a sequential element.

- Insertion Delay: The delay from the clock definition point to the clock pin of the register

|e-ISSN: 2319-8753, p-ISSN: 2347-6710| www.ijirset.com | Impact Factor: 8.423| A Monthly Peer Reviewed & Refereed Journal |

|| Volume 13, Issue 5, May 2024 ||

Fig.2.clock tree synthesis stage

#### TABLE III

RESULT OF SLACK ,SKEW ,LATENCY ,LEAKAGE POWER,INSERTION DELAY AT CTS STAGE.

| Cell               | HVT         | RVT         | LVT      |

|--------------------|-------------|-------------|----------|

| Gate Count         | 117610      | 118853      | 118714   |

| Slack (late)       | -3056 ps    | -859 ps     | -690ps   |

| Insertion<br>Delay | 1583 ps     | 1382 ps     | 1404 ps  |

| Skew               | 318 ps      | 277 ps      | 167 ps   |

| Latency            | 1511 ps     | 1314 ps     | 1154 ps  |

| Slack (early)      | -356 ps     | -277 ps     | -126 ps  |

| Leakage<br>Power   | 556.8<br>uW | 680.1<br>uW | 859.8 uW |

Table 3 shows the results at CTS (Clock Tree Synthesis) stage. CTS is done with the using only HVT cells, LVT cells and RVT cells. From this Table 3,

1) If CTS is done with only HVT cells then delay of that path will be more but leakage power is less than other two cells.so here leakage power is controlled.

L C A

|e-ISSN: 2319-8753, p-ISSN: 2347-6710| <u>www.ijirset.com</u> | Impact Factor: 8.423| A Monthly Peer Reviewed & Refereed Journal |

|| Volume 13, Issue 5, May 2024 ||

#### | DOI:10.15680/IJIRSET.2024.1305569 |

2) It CTS is done with only RVT cells then delay and leakage both will increase

3) If CTS is done with only LVT cells then delay of that path is controlled ,but leakage power increases.

So best way is to use LVT cells to build CLOCK TREE.

#### **III.**CONCLUSION

In this paper, we haveproposed the methodology to combine placement, gate sizing, and multiple-Vt cell swapping algorithms for leakage and total power optimization. The proposed simplistic power optimization script based on Flow experiments using multiple Vt technique and multivt swapping at synthesis stage achieved not only maximum sub threshold power benefits, but also met circuit speed and area reduction to the design. At Synthesis stage best way is to use the HVT and LVT cells using the multi v swapping flow. At CTS stage best way is to use LVT cells to build clock tree. This methodology can find the best optimal trade-off point between power and delay keeping the performance of the nanometer design.

#### REFERENCES

[1] W. Chuang and S. S. Sapatnekar, "Power vs. delay in gate sizing: Conflicting objectives," in *Proc. ICCAD*, pp. 463–466, Nov. 1995.

[2] W. Choi and K. Bazargan, "Incremental placement for timing optimization," in Proc. ICCAD, p. 463, 2003.

[3] Advanced ASIC chip Synthesis using Synopsis design Compiler ,Physical compiler and Prime Time.

[4] CMOS Digital Integrated Circuit Analysis and design by Sung mokang and Yusuf Leblebici

[5] C. Chu and D. Wong, "Vlsi circuit performance optimization bygeometric programming," in Annals of Operations Research, pp. 105:37–60, 2001.

[6] B. Hu, H. Jiang, Q. Liu, M. Marek-Sadowska, "Synthesis and placement flow for gain-based programmable regular fabrics", ISPD 2003, pp. 197-203.Structured ASIC synthesis with logical effort consideration by using a conventional cell-based design flow.

[7] S.Narendra , D. Blaauw, A.Devgan, and F. Najm, "Leakage issues in IC Design: Trends, Estimation and Avoidance, ICCAD 2003.

[8] P. Meinerzhagen, S. Sherazi, A. Burg, and J. Rodriguez, "Benchmarking of standard-cell based memories in the sub- domain in 65-nm CMOS technology," IEEE J. Emerging and Sel. Topics Circuits and Syst., vol. 1, no. 2, pp. 173–182, Feb. 2011.

[9]KimiyoshiUsami ; ShunsukeKogure ; Yusuke Yoshida ; Ryo Magasaki ; Hideharu Amano "Level-shifter free approach for multi-Vdd SOTB employing adaptive Vt modulation for pMOSFET "2017 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S)

[10]Ruqiang Bao ; Huimei Zhou ; Miaomiao Wang ; Dechao Guo ; Bala S Haran ; Vijay Narayanan ; Rama Divakaruni "Extendable and Manufacturable Volume-less Multi-Vt Solution for 7nm Technology Node and Beyond" 2018 IEEE International Electron Devices Meeting (IEDM)

[11] M. H. Liao and P. G. Chen, "The demonstration of the Si nano-tube device with the promising short channel control," J. Appl. Phys., vol. 118, no. 13, pp. 1–4, 2015.

[12] A. K. Jain, S. Sahay and M. J. Kumar, "Controlling LBTBT in Emerging Nanotube FETs Using DualMaterial Gate," in IEEE Journal of the Electron Devices Society, vol. 6, pp. 611-621, 2018.

INTERNATIONAL Standard Serial Number India

## INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

www.ijirset.com