e-ISSN: 2319-8753 | p-ISSN: 2347-6710

DIA

International Journal of Innovative Research in SCIENCE | ENGINEERING | TECHNOLOGY

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

Volume 13, Special Issue 1, April 2024

INTERNATIONAL STANDARD SERIAL NUMBER INDIA

# Impact Factor: 8.423

9940 572 462

6381 907 438

🖂 ijirset@gmail.com

International Journal of Innovative Research in Science, Engineering and Technology An ISO 3297: 2007 Certified Organization Volume 13, Special Issue 1, April 2024 11th National Conference on Frontiers in Communication & Signal Processing Systems (NCECSPS '24)

11<sup>th</sup> National Conference on Frontiers in Communication & Signal Processing Systems (NCFCSPS '24) 25<sup>th</sup> - 26<sup>th</sup> April 2024

Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

# Industrial Methodology of Verification of 32\*8 RAM with Different Testcases Using Verilog

Mr. E. Sakthivel<sup>1</sup>, Prasanth R<sup>2</sup>, Thangamani S<sup>3</sup>, Vasanth kumar N<sup>4</sup>, Kavish M<sup>5</sup>

Assistant Professor, Department of Electronics and Communication Engineering, Adhiyamaan College of Engineering,

Krishnagir, Tamil Nadu, India<sup>1</sup>

U.G Scholars, Department of Electronics and Communication Engineering, Adhiyamaan College of Engineering,

Krishnagiri, Tamil Nadu, India<sup>2, 3, 45</sup>

**ABSTRACT:** This project is about designing a 32\*8 random access memory and verifying the RAM using Verilog programming language.it is a hardware description language used to model the electronic systems and to describe digital systems and circuits in the form of code. At present industrial professionals are trying to design and verify the digital systems which should be easier and simpler to use. This project allows us to design and verify the RAM in a easier and simpler methodology by using five different test cases. The designing undergoes by using the register transfer level codes which can be verified by the test bench in a behavioural level of abstraction by using task, functions and arrays.

KEYWORDS: RTL design and verification, RAM, Verilog, Digital design, Test bench

## I. INTRODUCTION

The verification of a 32x8 RAM module using Verilog is a crucial aspect of digital The design validation. RAM (Random Access Memory) plays a fundamental role in computer systems, storing data in a manner that allows for rapid access to any location within the memory. Verifying the functionality of a RAM module ensures that it operates correctly according to its design specifications and requirements. This project focuses on verifying the behavior of a 32x8 RAM module implemented in Verilog HDL (Hardware Description Language). The RAM module comprises a set of input and output ports, including clock, reset, read enable, write enable, address, data input, and data output. By simulating different test cases, we aim to validate the RAM module's performance under various scenarios, ensuring its correctness and reliability in practical applications. Through this verification project, we aim to demonstrate the effectiveness of using Verilog for digital design verification and highlight the importance of rigorous testing in ensuring the reliability and functionality of complex digital system.

## **II. EXISTING SYSTEM**

The existing system likely involves traditional methods for verifying RAM modules, which may include

- manual testing

- simulation-based verification

- Limited Functional Coverage

- Difficulty in Debugging

While these methods may have been effective to some extent, they may also possess certain limitations or demerits

ISSN (Online) : 2319 - 8753 ISSN (Print) : 2347 - 6710

Volume 13, Special Issue 1, April 2024

## International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization

11th National Conference on Frontiers in Communication & Signal Processing Systems (NCFCSPS '24)

# 25<sup>th</sup> - 26<sup>th</sup> April 2024

#### Organized by

#### Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

#### **III. PROPOSED SYSTEM**

- By adopting the proposed system, designers can overcome the limitations of traditional verification methods and ensure the correctness and reliability of RAM modules in complex digital designs.

- Simulation Acceleration

- Advanced Debugging Capabilities

- Enhanced Functional Coverage

- Scalability and Reusability

- Improved Verification Productivity

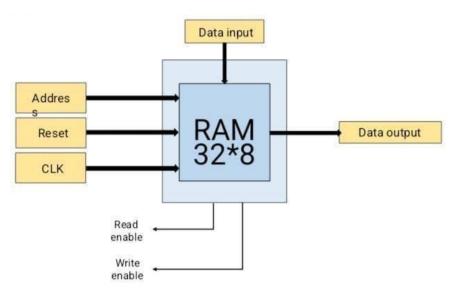

#### **IV. BLOCK DIAGRAM**

#### V. WORKING PRINCIPLE

The design and verification of the RAM 32\*8 include the following principle,

In Verilog, the design code is used to synthesis the actual hardware description of a digital circuit, specifying its behavior or structure. This code describes how the circuit should operate or how its components should be interconnected.

The module RAM 32\*8 is declared with clock(clk), reset (rst), address (addr), write enable (wr\_en), read enable (rd\_en), data input (data\_in), and data output (data\_out) ports. Inside the module, there's an array memory declared to store 32 8-bit words. Each word corresponds to an address (0 to 31).

| Wr_en | Rd_en | Data_in | Data_out |

|-------|-------|---------|----------|

| 0     | 0     | 0       | X        |

| 0     | 1     | Х       | Data_in  |

| 1     | 0     | data    | x        |

| 1     | 1     | Data_in | data     |

#### International Journal of Innovative Research in Science, Engineering and Technology Volume 13, Special Issue 1, April 2024

An ISO 3297: 2007 Certified Organization

11th National Conference on Frontiers in Communication & Signal Processing Systems (NCFCSPS '24)

# 25<sup>th</sup> - 26<sup>th</sup> April 2024

**Organized** by

#### Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

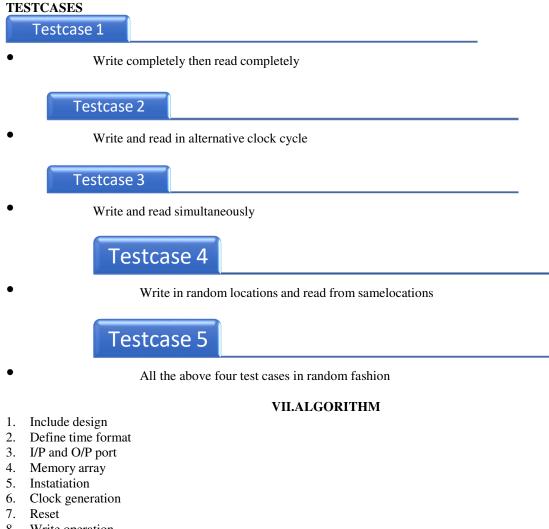

#### VI. TEST BENCH

A testbench code, on the other hand, is used to simulate and test the design code. It provides stimulus to the design under test (DUT) and checks its responses to ensure that it behaves as expected. The testbench typically contains input stimuli, which are applied to the inputs of the DUT, and assertions or checks to verify that the outputs of the DUT are correct. This test bench verifies the basic functionality of a 32x8 RAM by writing data to address 0 and then reading it back. It's important to extend this test bench to cover various address and data scenarios comprehensively verify the RAM functionality.

- Write operation 8.

- Compare 9.

- 10. Verify

Volume 13, Special Issue 1, April 2024

#### International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization

11th National Conference on Frontiers in Communication & Signal Processing Systems (NCFCSPS '24)

25<sup>th</sup> - 26<sup>th</sup> April 2024

Organized by

#### Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

## VIII. FLOW CHART

#### **IX. CONCLUSION**

In conclusion, the industrial verification of RAM 32x8 using Verilog has been successfully completed, demonstrating the functionality and reliability of the design. Through rigorous testing and verification processes, it has been shown that the RAM module operates as intended, meeting the specified requirements and standards. This project not only validates the effectiveness of Verilog in designing complex digital systems but also highlights the importance of thorough verification in ensuring the integrity of industrial-grade components. Moving forward, the insights gained from this project can contribute to the advancement of digital design methodologies and serve as a foundation for future developments in the field of hardware verification and design.

#### REFERENCES

- 1. "Principles of CMOS VLSI Design: A Systems Perspective" by Neil H. E. Weste and David Money Harris: While focusing on CMOS VLSI design, this book discusses memory design principles and implementation techniques.

- 2. "Digital Design and Computer Architecture" by David Money Harris and Sarah L. Harris: This book provides a comprehensive introduction to digital design concepts and Verilog programming, including memory design.

- Digital Integrated Circuits: A Design Perspective" by Jan M. Rabaey, Anantha Chandrakasan, and Borivoje Nikolić: This book covers various aspects of digital integrated circuits, including memory design principles and implementations.

- "CMOS Digital Integrated Circuits: Analysis and Design" by Sung-Mo Kang and Yusuf Leblebici: This book

provides a comprehensive overview of CMOS digital integrated circuits, including memory design considerations

andarchitectures.

- 5. "Memory Systems: Cache, DRAM, Disk" by Bruce Jacob, Spencer Ng, and David Wang: Although broader in scope, this book offers detailed insights into memory systems, including RAM design principles and optimization

ISSN (Online) : 2319 - 8753 ISSN (Print) : 2347 - 6710

# International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization

Volume 13, Special Issue 1, April 2024

11th National Conference on Frontiers in Communication & Signal Processing Systems (NCFCSPS '24)

25<sup>th</sup> - 26<sup>th</sup> April 2024

Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

techniques.

#### BIOGRAPHY

Mr.E.Sakthivel, Assistant Professor, Electronics and CommunicationEngineering Department, Adhiyamaan college of Engineering, Hosur

Prasanth.R, Electronics and CommunicationEngineering Department, Adhiyamaan college of Engineering, Hosur

Thangamani.S, Electronics and CommunicationEngineering Department, Adhiyamaan college of Engineering, Hosur

Vasanth kumar.N, Electronics and CommunicationEngineering Department, Adhiyamaan college of Engineering, Hosur

Kavish.M, Electronics and CommunicationEngineering Department, Adhiyamaan college of Engineering, Hosur

# International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified OrganizationVolume 13, Special Issue 1, April 202411th National Conference on Frontiers in Communication & Signal Processing Systems (NCFCSPS '24)

25<sup>th</sup> - 26<sup>th</sup> April 2024

# Organized by

#### Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

Thangamani.S,

Electronics and CommunicationEngineering Department, Adhiyamaan college of Engineering, Hosur

INTERNATIONAL Standard Serial Number India

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

www.ijirset.com